静态随机存储器(SRAM)作为一种典型的半导体器件,已被广泛的应用于计算机、手机、数码相机等电子设备中。

随着半导体技术的发展,存储器的制备工艺也越来越成熟,同时所形成的存储器也具备更好的性能。在实际的生产场景中,部分厂商利用鳍式效应晶体管来作为存储器中的晶体管器件。虽然将鳍式场效应晶体管应用于存储器中,有利于缩减存储器的尺寸,并且还可提高存储器的性能。然而,存储器的性能还需进一步优化,例如改善存储器的读取容限等。

为此,中芯国际在2017年5月9日申请了一项名为“存储器及其形成方法”的发明专利(申请号:201710322968.X),申请人为中芯国际集成电路制造(上海)有限公司。

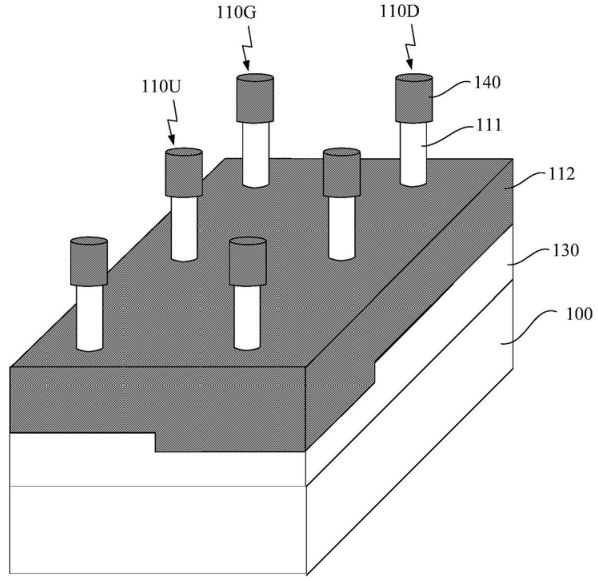

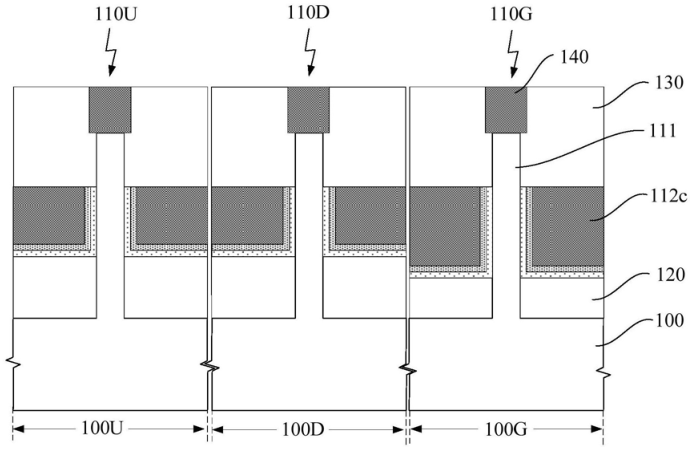

如上图,为该专利中发明的存储器的结构示意图,存储器包括衬底100、下拉晶体管(PD)110D和传输门晶体管(PG)110G,其中下拉晶体管和传输门晶体管均设置在衬底上,衬底的材料通常选用硅、锗或者锗硅混合形式,且传输门晶体管的沟道区域的长度L1大于下拉晶体管的沟道区域的长度L2。

此外,在存储器上还包括有上拉晶体管(PU)110U,其为具有环绕式栅极的晶体管器件,例如环绕式栅极纳米线场效应晶体管(GAA NWFET)。在上拉晶体管内还包括有纳米柱111和栅极结构112,纳米柱构成了晶体管的源区和漏区。

在这种结构中,只要使传输门晶体管的沟道区域的沟道长度L1大于下拉晶体管的沟道区域的沟道长度L2,就可以增大下拉晶体管的沟道电流与传输门晶体管的沟道电流的比值。从而提高存储器的β比率,有利于改善存储器的读取容限。

如上图,为该存储器的剖面示意图,栅极结构还包括有栅介质层112a、功函数层112b、栅极电极层113c和隔离层120,栅介质层形成于纳米柱的侧壁,由高K介质层(氧化铪层或氧化铝层)组成。隔离层设置在衬底上,并将纳米柱的外围进行了填充,使得多个纳米柱之间相互隔离、避免串扰。

而除了使得L1大于L2以外,还可在不同区域上直接形成具有不同厚度的栅极结构,以对应形成不同长度的沟道。例如,当第一隔离层的上表面的高度位置一致时,则可直接在传输门晶体管对应区域的隔离层上形成第一厚度的栅极结构,在下拉晶体管对应区域的隔离层上形成第二厚度的栅极结构,并使得第一厚度大于第二厚度。如此一来,也可使传输门晶体管的沟道长度大于下拉晶体管的沟道长度。

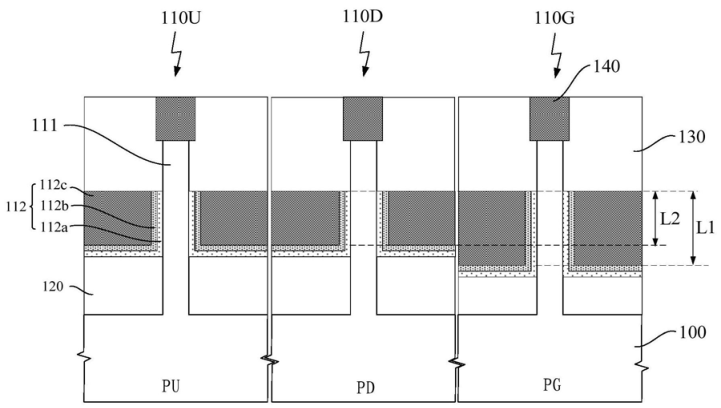

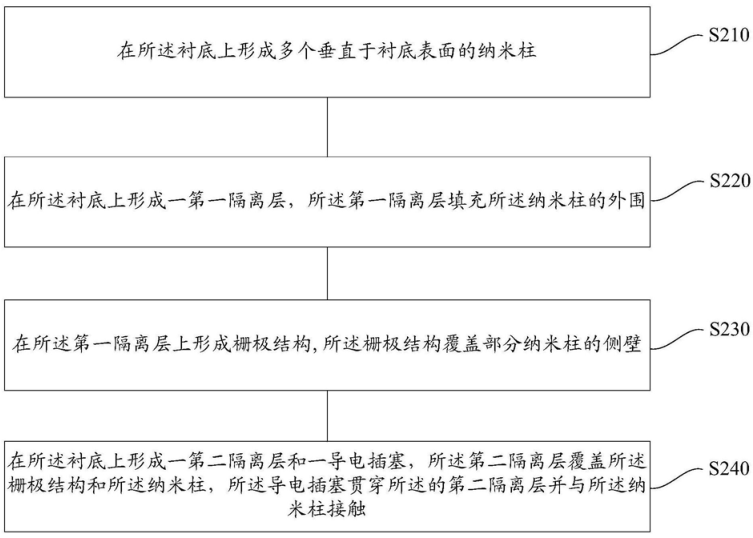

如上图,为上述这种存储器的形成方法的流程示意图,其主要是在衬底上形成下拉晶体管和传输门晶体管,这两个晶体管均为具有环绕式栅极的晶体管器件。例如,下拉晶体管和传输门晶体管为N型晶体管,上拉晶体管为P型晶体管。

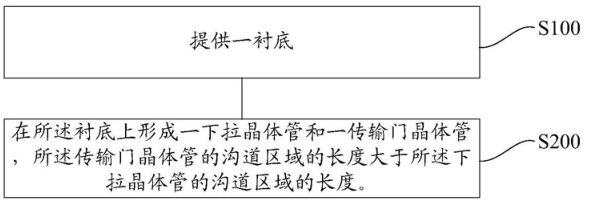

因此,可以看到,该存储器中的晶体管器件是较为重要的一个环节。如上图,为该方案制作晶体管的流程示意图,首先,需要在衬底上划分好用于形成传输门晶体管的第一区域、用于形成下拉晶体管的第二区域以及用于形成上拉晶体管的第三区域。

接着,在衬底上形成垂直于衬底表面的纳米柱以及第一隔离层,第一隔离层包围在纳米柱的外层,这些纳米柱相互隔离以避免串扰。最后,在隔离层上设置栅极结构,并在衬底上安置第二隔离层和导电插塞,使得第二隔离层与纳米柱相连接。

最后,上图为使用上述方法形成的存储器结构示意图,可以看到,衬底100上包含有第二隔离层130和导电插塞140,第二隔离层覆盖着栅极结构112和纳米柱111,导电插塞贯穿的第二隔离层并与纳米柱接触。在材料的选择上,第二隔离层通常为氧化层,导电插槽的材质选择为钨(W)。

以上就是中芯国际发明的具有传输门晶体结构的存储器方案,在该方案中,通过控制传输门晶体管的沟道区域长度,可以使得传输门晶体管的沟道电流小于下拉晶体管的沟道。从而有利于提高存储器的比率,进而改善存储器的读取容限。